# COMPARATIVE ANALYSIS OF MULTILEVEL INVETER IN POWER APPLICATION: A REVIEW

Darshana D. Khedkar

PG Scholer, Electrical Engineering Depertment SSBT's College of Engineering & Technology, Jalgaon.

Dr. P. V. Thakre

Professor, Electrical Engineering Department SSBT's College of Engineering & Technology, Jalgaon.

Abstract — This paper deals with various Multilevel Inverter topologies used in Renewable Energy Sources. Also, it deals with three phase Cascaded Multilevel Inverter and its control techniques and also modulation techniques for modular cascaded multilevel inverter. The Review paper is made in the aspects of Construction Complexity, Installation area, Total Harmonic Distortion, Controlling methodologies and Components required. The Multilevel Inverter (MLI) performance, reliability, efficiency not decided by the types and levels of MLI and but by the usable Pulse Width Modulation(PWM) techniques. Depends upon the usage of PWM techniques the THD value will also get varied and hence it is noted. This review paper will be more useful for selecting a suitable MLI and PWM Techniques for any Renewable Energy Sources. This paper is review of MLI in particular to the form and function of modular multilevel inverters (MMI), with their different topologies, modulation, modeling and control schemes. Detailed analysis of MMI with their functions and types has been made in comprehensive manner with existing literature available till now. All existing methods are compared in all manner in detail considering all parameters for applications of the best methods available.

Keywords — Multilevel Inverter, Hybrid Inverter, Cascaded Multilevel Inverter, PWM Techniques, Total Harmonic Distortion, Renewable Energy Sources.

### I. INTRODUCTION

Recently, the multilevel inverters have gained much attention due to their major effective and flexible features such as high power quality output waveform with low harmonic components, enhanced electromagnetic consistence, less circuit complexity, lower dv/dt ratio and reduction in switching losses. Although the two level inverter method of converting AC is effective but it has some drawbacks as it creates harmonic distortions in the output voltage waveform and also has a high dv/dt ratio as compared to that of a multilevel inverter. The MLI is a kind of updated version of two-level inverter. MLI creates a smoother stepped output waveform, it has lower dv/dt and also low harmonic distortions. When voltage level increases, the harmonic distortions will reduce accordingly, but the problems of complexity in implementation, controller circuit and electronics components, cost also increases along with the increased voltage levels. Also, in this paper , detailed study is made on Cascaded type of multilevel inverter and comparison is made for better application. In that, main focus is given to various techniques used for three phase cascaded multilevel inverter.

Researchers started to focus on Multilevel inverters especially in medium and high power applications due to its characteristics of providing staircase output voltage waveform with power semiconducting devices. MLI have an advantage of enabling the inter-connection of renewable energy sources to improve the energy utilization of the system. In order to improve the quality of the output voltage, the number of components required to implement three-phase CMLI should be significantly increased which increases the implementation cost, inverter physical size and complicates the control system. Although several topologies have been proposed in order to reduce the device count and increase the number of levels of single phase CMLIs, the majority of these topologies have not been extended to three-phase structure yet.

### II. THEORY

The paper titled as A Novel Concept for Three phase Cascaded Multilevel Inverter Topologies is studied.

The main challenge for multilevel inverter to maximize the number of voltage levels in the output is to have reduced number of components. The new concepts like device count reduction technique which is used to extend single phase cascaded MLI to three phase structures without tripping number of semiconductors and generalized technique which has concept of cascaded stage and phase generator stage.

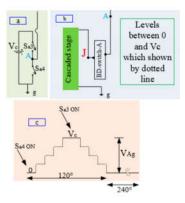

The diagram for proposed CMLI for generation of maximum and zero voltage levels, intermediate level generation, pole voltage is shown in fig 1.

Figure 1. Simplified structure of the proposed CMLI, (a) generation of maximum and zero voltage levels; (b) intermediate level generation; (c) pole voltage waveform.

| Table 1.Comparison between three-phase conversion of single-phase structure and proposed concept of device |

|------------------------------------------------------------------------------------------------------------|

| count technique                                                                                            |

|                                                                                     | Single Phase Structure |          |             | Conventional 3 Phase<br>Conversion |          |                    | This Paper Proposed<br>Concept |          |             |

|-------------------------------------------------------------------------------------|------------------------|----------|-------------|------------------------------------|----------|--------------------|--------------------------------|----------|-------------|

| Topology                                                                            | Line Voltage Levels    | Switches | DC-Supplies | Line Voltage Levels                | Switches | <b>DC-Supplies</b> | Line Voltage Levels            | Switches | DC-Supplies |

| Non-isolated inverter topology [9]<br>DC-link half-bridge cascaded<br>inverter [21] | 15                     | 12       | 7           | 15                                 | 36       | 21                 | 17                             | 24       | 8           |

|                                                                                     | 13                     | 12       | 6           | 13                                 | 36       | 18                 | 15                             | 24       | 7           |

From table 1, results are shown as while increasing levels in the output, the dc supplies and switches are reduced when single phase structure extended to three phase one. Also in this paper, comparison with other topologies is considered where size of three phase MLI is reduced, less number of power semiconductor components, number of gate driver circuits and number of DC supplies to show the effectiveness of proposed topology.

Table 2.Comparison among conventional three-phase CHB topologies and proposed three-phase cascaded MLI for different asymmetric input voltage arrangements

|                              | Binary Related Two CHB<br>Cell Topology [35] |                      |                  | ed Three CHB<br>ology [42] | Trinary Related Four CHB<br>Cell Topology [38] |                      |

|------------------------------|----------------------------------------------|----------------------|------------------|----------------------------|------------------------------------------------|----------------------|

| Category                     | Existing 3-Phase                             | Proposed New Concept | Existing 3-Phase | Proposed New Concept       | Existing 3-Phase                               | Proposed New Concept |

| No of levels in line voltage | 7                                            | 9                    | 27               | 29                         | 81                                             | 83                   |

| No of switches               | 24                                           | 20                   | 36               | 24                         | 48                                             | 28                   |

| No of diodes                 | 24                                           | 20                   | 36               | 24                         | 48                                             | 28                   |

| No of gate driver            | 24                                           | 20                   | 36               | 24                         | 48                                             | 28                   |

| No of dc supplies            | 6                                            | 3                    | 9                | 4                          | 12                                             | 5                    |

When the new three-phase cascaded MLI concept is applied to these existing topologies, device count is reduced which can be realized in Table 2. As the number of CHB cells in each phase arm is going to increase, the percentage of reduction of device count and the input dc supplies is increasing.

The total conduction and switching losses of all used semiconductors calculates the semiconductor losses of proposed CMLI as below

$$P_{total loss} = P_{c}(t) + P_{sw} \dots \dots \dots (1)$$

And, inverter efficiency can be calculated from Pout as

$$\eta\% = \left(\frac{Pout}{Ptotal\ loss+Pout}\right) *\ 100\% \quad \dots \dots (2)$$

The three phase cascaded MLI used new technique which is cost effective since less number of components which helps to reduce cost, complexity and installation area, switching losses, improve efficiency. Hence, this new technique used in this paper have great potential for renewable power generation system and smart grid applications[6].

The paper titled, 'Novel Three Phase Multilevel Inverter Topology with Symmetrical DC Voltage Sources' is studied where sinusoidal pulse width modulation (SPWM) and staircases modulation are effectively executed. This paper presents new circuit having reduced number of components count keep in the same pole voltage levels number. A new proposed circuit of multilevel inverter have several features as reduced DC voltage sources, high utilization factor of DC voltage sources, reduced power switches and control execution, simplicity. Also, two modulation schemes are introduced to produce semi like sinusoidal voltage waveforms across output terminals.

Low Frequency Modulation Schemes - In this, frequency of switching pulses is very low due to which switching losses are reduced.

Sinusoidal Pulse Width Modulation - In this, three signals are used which is shifted from each other by 120 degree called modulation signals which is compared with multicarrier signals with frequency 50Hz. The distortion factor and lower order harmonics are reduced significantly. The gating signals are generated by comparing a sinusoidal reference signal with a triangular carrier wave of frequency Fc. The frequency of reference signal Fr ,determines the inverter output frequency and its peak amplitude Ar, controls the modulation index M, and rms output voltage Vo. The number of pulses per half cycle depends on carrier frequency . Also In this, Phase Disposition(PD) modulation schemes is used. Due to limitation of increasing inverter size, reducing life time of the system, complexity, electrolyte capacitors and power diodes not used[2].

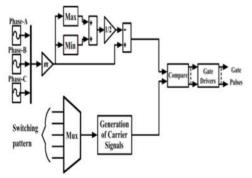

The paper titled 'Three Phase Cascaded Multilevel Inverter operated with Switching Frequency Optimal Technique' is studied. In this, reduced switch count topology and switching frequency optimal (SFO) technique is used. SFO modulation scheme is utilized to allow improvement in the output voltage and provide low content of output harmonic distortions at the output. By adding an offset to sinusoidal reference waveforms, we can achieve modulating signals. The block diagram for SFO technique is shown in fig 2. Here, phase disposed triangular signals are used as carrier to generate PWM signals.

Fig 2 Proposed inverter topology

Fig 3 Gate Pulse generation logic / block diagram of SFO technique

Single module with symmetric source configuration - In this, two sources for each phase is considered and considered for 5 level.

Single module with asymmetric source configuration - In this, two sources are considered in 1:2 ratio and seven level was obtained in output voltage.

Cascaded case with symmetric source configuration - In this, two modules are cascaded in series in each phase and nine level output voltage was obtained.

Cascaded case with asymmetric source configuration - In this, binary source configuration was used and thirtyone voltage levels in each phase was obtained.

| NUMBER OF LEVELS IN<br>OUTPUT VOLTAGE PER | THD<br>VALUES IN LINE |

|-------------------------------------------|-----------------------|

| PHASE                                     | VOLTAGE(%)            |

| 5                                         | 10.16                 |

| 7                                         | 6.16                  |

| 9                                         | 5.64                  |

| 31                                        | 1 77                  |

Table 3. THD values for above four cases

It is observed from the result that the output voltage increases, THD decreases which improves the number of levels in the output voltage. This paper concludes reduced component count for number of voltage levels which means THD is reduced with minimum switches[1].

The paper titled, 'Power Quality Improvement of the System using Three Phase Cascaded H-Bridge Multilevel Inverters' is studied which is focused on reduction of THD with the increasing levels of Cascaded Multilevel Inverters. In this, THD of 5 level and 15 level cascaded H bridge inverter is compared. It is observed that as level increases in MLI, complexity increases but losses are reduced in higher level inverters. For renewable energy environment, harmonic free supply is mostly needed for better power quality, high efficiency which is achieved by higher level multilevel inverters. Also, due to higher sensitive equipments used in power systems, power quality issues are stronger and to solve this issue, IGBT is used here for better output and efficient operation of inverter due to its operational characteristics.

| •a                                      | † <i>b</i>                          | 1 c                                     |

|-----------------------------------------|-------------------------------------|-----------------------------------------|

| + + +++++++++++++++++++++++++++++++++++ | + \$ \$ +                           | + + +++++++++++++++++++++++++++++++++++ |

| = V <sub>dcal</sub> V <sub>al</sub>     | = V <sub>dcb1</sub> V <sub>b1</sub> | + Vdee1 Vet                             |

| · +\$ +\$                               | · ≰≩ ≰≩·                            | · K K                                   |

| + + +++++++++++++++++++++++++++++++++++ | + 5 5+                              | + 5 5+                                  |

| $= v_{dva2}$ $v_{a2}$                   | w Vakeb2 Vb2                        | * V <sub>dcc2</sub> V <sub>c2</sub>     |

| · K} K}                                 | · 🗱 🗱 ·                             | · 🚯 🚯                                   |

| + + +++++++++++++++++++++++++++++++++++ | + 14 14+                            | + 5 5+                                  |

| = Veleum Verm                           | W Vdchm Vhm                         | * Vdccm Vcm                             |

| · \$\$ \$\$.                            | · 4 4                               | · K} K}.                                |

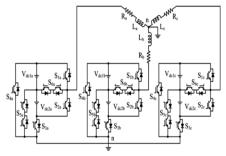

Fig 4.Basic circuit topology of 3-phase cascaded H-bridge MLI for m-levels

Fig 5. Pulse generation circuit for 5-level cascaded H-bridge multilevel inverter

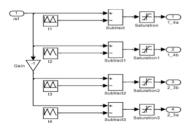

Matlab model for generating control signals for 5-level CHBMLI is shown in fig 5 where increasing carrier signals, same concept can extend up to several levels in future.

Cascaded H-bridge MLI used to compensate current and voltage harmonics using different compensation techniques which are traditional and modified. Higher order MLI should be used to provide harmonic free supply voltage for better power quality and efficiency[8].

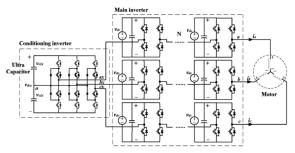

The paper titled, 'Investigation of Control Method for a New Hybrid Cascaded Multilevel Inverter' is studied and analysed. In this, hybrid cascaded multilevel inverter's structure is analysed and observed. In this, it introduces hybrid cascaded multilevel inverter which is the combination of main inverter and conditioning inverter. The main inverter implies H bridge inverter and Conditioning inverter implies 3 level diode clamped inverter where both are combined together to drive the motors. The main inverter needs DC voltage source. Ultra capacitors are used to store the braking energy of motors which is reused supply the conditioning inverter. Also, maintaining the same voltage output, the scheme used in this reduce the dc sources other than traditional H- bridge inverter[7].

Fig 6. Circuit diagram of hybrid multilevel inverter

Control of Hybrid Cascaded Multilevel Inverter - There are several advantages of Hybrid multilevel inverter based on main inverter. The conditioning inverter can store and reuse the braking energy that is energy storage device results in improved inverter efficiency. The conditioning inverter improve power factor of the system. Control of conditioning inverter voltage - With an appropriate control algorithm, its capacitor voltages have to be stabilized. Without appropriate control, non-supplied capacitor voltages will vary from their nominal values. Balance of Capacitor Bank Voltage and Management of Capacitor Energy

In this paper, though combination of two inverters are used, but resulting waveform produce good power quality. Control of both hybrid cascaded inverter and conditioning inverter are detailed studied. Without deteroiting output voltage, control method needed to stabalize voltages. Also, this topology found great applications in accelerating and braking of motors.

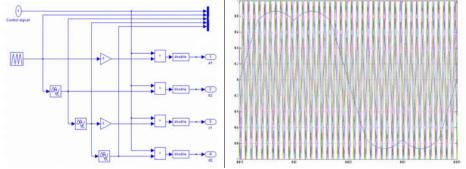

The paper titled, "Control of Three Phase Cascaded Multilevel Inverter Using Various Novel Multicarrier Pulse width Modulation Techniques" provides analysis of various novel pulse width modulation techniques. This techniques are used to enhance the output voltage to multilevel topologies. Multilevel inverters have wide application in power electronics like ups, flexible ac transmission system (facts), active filters etc. There are different methodologies discussed in this paper, the switching frequency optimal methodology analysed by the novel multicarrier pulse width modulation techniques. In this paper, the three novel multicarrier produced to utilize the special properties of multilevel inverter. Constant switching frequency multicarrier, Switching frequency optimal pulse width modulation, Variable Switching Frequency Multicarrier switching frequency optimal pulse width modulation are discussed and compared with each other based on THD. Before modulation or pulse dropping occurs, it enables modulation index to increase by 15%. By third harmonic injection, MC-SFO is used to increase output voltage.

VSFMC-SFO PWM signal generation enhance output voltage by 15% and harmonics are not increased.

Fig 7. PSC-SFO PWM signal generation and its waveform

The carrier voltage shown is average of maximum and minimum value of Va,Vb,Vc. The difference between reference voltages to carrier voltage is phase voltage with SFO concept. The zero sequence modification made by the SFO PWM technique is not used for three phase three wire system. And hence in phase shifted SFO PWM, modulation index increased by 15% before any occurance of over modulation and pulse drooping[3].

| Modulation<br>Index | CSMC-S<br>PWM | FO VSMC-SFO<br>PWM |       | PSC-SFO PWN | ſ     |                   |

|---------------------|---------------|--------------------|-------|-------------|-------|-------------------|

|                     | THD%          | Vac                | THD%  | Vac         | THD%  | V<br>ac           |

| 1.0                 | 21.7          | 10.2               | 22.82 | 10.2        | 20.92 | 1<br>1.43         |

| 0.9                 | 21.3          | 10.0               | 22.47 | 10.0        | 20.65 | 1<br>1.01         |

| 0.8                 | 20.9          | 09.86              | 22.18 | 09.82       | 20.51 | 1<br>0.04         |

| 0.7                 | 21.5          | 09.51              | 22.71 | 09.75       | 20.72 | 9.32 <sup>0</sup> |

Table 4. Output voltage of various modulation index and THD

Table 4 shows the modulation index and THD with respect to different schemes and results are obtained by comparision. In this paper, the technique used for multilevel inverter has improved output voltage and reduce output THD.

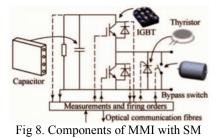

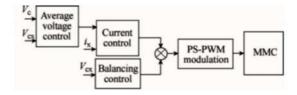

The paper titled, "Analysis of the Phase-Shifted Carrier Modulation for Modular Multilevel Inverters" is studied. The concept of capacitor voltage balancing and circulating current suppression for the implementation modular multilevel inverter is studied in this paper. The pulse width modulation harmonic characteristics of output voltage and circulating current is identified in this paper for the study of phase shifted carrier modulation. To improve the performance of modular multilevel inverter, several mathematical analysis, modelling methods under different conditions are performed and also several control solutions are proposed. In this, mainly NLC is prefered for the modular multilevel inverter due to more number of sub-modules. Due to various features, the phase shifted analysis are most suited to multilevel inverter such as

Capacitor voltage balancing is gained with the evenly distribution of sub-modules.

Modularity and Scalability is observed by each triangular carrier to sub-module.

THD is obtained less in output voltage.

Keeping in mind, the above advantages, many researchers directly preferred Phase Shifted Carrier (PSC) Technique for Cascaded Modular Multilevel Inverter which is further detailed study is introduced in this paper. Also, the other main attension is on voltage harmonics and circulating current harmonics where both are identified by optimum displacement angles with the analysis of double Fourier series. It is also found that dc link voltage vary in wide range and hence it is most suitable for renewable energy applications. MMI with full bridge sub-modules has found its applications in HVDC because it is able to cut off short circuit current and reverse the dc link voltage polarity. In this paper, overall the operating principles and theoretical analysis for PSC modulation scheme is studied. Also extension to PSC scheme is achieved to reduce the size of filters and raise the switching frequency. From this paper, it is concluded that phase shifted modulation scheme is effective PWM scheme for MMIs[6].

The paper titled as "Recent advances in Multilevel Inverters and their Applications" is studied. In this paper, most recent advances for multilevel inverter to achieve efficiency in its operation, reduce switching and conduction losses in output voltage an different modulation techniques and control methods are introduced

and studied. In this, new structures for cascaded multilevel inverters are observed in which less electronics components, diodes, gate driver circuits are required. Also, various PWM techniques for single phase, three phase inverters are indentified. In this paper, features and applications of modular multilevel inverter is discussed[9].

The paper titled, "Overview on Reliability of Modular Multilevel Cascade Inverters" is studied where in this details of family members of MMC inverter is explained.

In this, the reliability of Modular Multilevel Cascaded Inverter (MMCI) aimed to improve the reliability of MMCC, including redundancy design, fault diagnosis, fault-tolerant control is explained. In this paper, the reliability issues of MMCC and current research are discussed. The study of the conventional methodology for the reliability estimation and measures to improve reliability. The failure cases of the power electronics converters, the reliability evaluation methodology for MMCI, measures to improve reliability of MMCI from the design phase to the operation phase, challenges and opportunities for the reliability issue of MMCI are surveyed and analyzed. The principle that the circulating current is used to reduce the capacitor voltage fluctuation and balance the capacitors' voltages output current so as to control to satisfy the requirement of the given operating condition. These principles are same for other family members of MMCI. The modular multilevel converter in hexagonal configuration called "hexverter" which uses 6 branches of full-bridge sub modules SMs. The capacitor voltages can be balanced by adjusting the circulating currents and common mode voltage and hence fluctuation reduced[4].

The peripheral components are similar but different topologies such as the full-bridge SM, asymmetrical double commutated SM, cross- or parallel- connected, clamped-double, the FC and NPC SM. The hybrid design with the half-bridge and other bipolar SMs can be used so as to optimize the design in terms of DC fault handling capability, efficiency and cost, considering different features of various SM circuit configurations. The simple half- bridge SM seems best regarding reliability and the hybrid design seems better regarding reliability and cost. Also, there are two categories of capacitor voltage balancing control methods: balancing control prior to the carrier phase shift (CPS) modulation; balancing control by the sorting algorithm after the staircase modulation where the CPS modulation is too complex and the staircase modulation can be preferred.

Fig 9. (a) Balancing control to CPS modulation by adjusting reference

(b) Capacitor voltage balancing by sorting algorithm after staircase modulation

Evaluation of modular multilevel cascade converters reliability - Considering the features of modularity and redundancy, methodology to calculate reliability is modified while estimating reliability of MMCI. Failure rate and reliability calculation methods - The failure rate is the mean number of failures per unit time, which indicate "proneness to failure" of an item.

A) Reliability calculation of MMCI - Three steps are used first to calculate the SM's reliability based on the Markov-chain model then calculate cluster level and lastly system level reliability based on k-out-of-n model. B) Lifetime estimation - This lifetime prediction method involves the physical IGBT models and the electrical-thermal simulation.

Possible measures to improve reliability of MMCI

A)Parameter selection on reliability - The concept of the systematic safe operating area (SSOA) for designing reliable power converters and SM design to improve the reliability compared to device's SOA.

B)Redundancy design, fault diagnosis and tolerant control - They are the major measures for MMCI to improve the reliability which is researched extensively that is a complete fault handling process of MMC is provided. C)Reliability-oriented design procedure of MMCI - This can increase the reliability, and also the system whole life cycle cost is reduced[4].

## **IV. CONCLUSION**

As seen, multilevel inverters achieved their horizon of in various fields of application as industrial, renewable energy, hvdc applications etc. Mostly they are used in industry for medium and high voltage applications. The main purpose of MLI is to provide limit over the total harmonic distortion (THD), electromagnetic interference (EMI), voltage stress on the switches and dv/dt problems and hence it is mostly preferred in recent concepts due to its benefits. From this paper, it is concluded that three phase cascaded multilevel inverter has many great features related to harmonics, reliability, less components, restricts voltage balancing problems. Also, the different techniques as switching frequency optimum technique, multicarrier pulse width modulation technique, phase shifted carrier modulation technique required for three phase cascaded multilevel inverter is studied and compared. It is also concluded that the three phase cascaded multilevel inverter play great role in power quality improvement. It is useful for improved power quality. Also, It is found and concluded the best control method for hybrid cascaded multilevel inverter from investigation of other controlling techniques.

#### REFERENCES

- [1] Reshma Krishnan R, Vijay B. Borghate, Rajat T. Shahane, Santosh Kumar Maddugari, Sidharth Sabyasachi, M. Tech Scholar, Visvesvaraya National Institute of Technology Nagpur, India, "A Three Phase Cascaded Multilevel Inverter Operated with Switching Frequency Optimal Technique", 978-1-5386-2462-3/18-2018 IEEE.

- [2] Ahmed Salem, Emad M. Ahmed, Mahrous Ahmed and Mohamed Orabi, IEEE Senior Member APEARC, Faculty of Engineering, Aswan University, Aswan 81542, "Novel Three Phase Multi-Level Inverter Topology with Symmetrical DC-Voltage Sources", 978-1-4673-9550-2/16 2016 IEEE.

- [3] Subhransu Sekhar Dash, Department of Electrical and Electronics Engineering SRM University Chennai, India, "Control of Three Phase Cascaded Multilevel Inverter Using Various Novel Multicarrier Pulse Width Modulation Techniques".

- [4] Zhengming Zhao, Kai Li, Ye Jiang, Sizhao Lu, and Liqiang Yuan, Tsinghua University, Beijing, China, "Overview on Reliability of Modular Multilevel Cascade Inverters", Chinese Journal of Electrical Engineering, Vol.1, No.1, December 2015.

- [5] Md Mubashwar Hasan, A. Abu-Siada, Syed M. Islam and S. M. Muyeen Department of Electrical and Computer Engineering, Curtin University, Perth, Australia, "A Novel Concept for Three-Phase Cascaded Multilevel Inverter Topologies"; Received: 16 November 2017; Accepted: 15 January 2018; Published: 23 January 2018.

- [6] Binbin Li, Rongfeng Yang, Dandan Xu, Gaolin Wang, Member, IEEE, Wei Wang, and Dianguo Xu, Senior Member, IEEE, "Analysis of the Phase-Shifted Carrier Modulation for Modular Multilevel Inverters", IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 30, NO. 1, JANUARY 2015.

- [7] Jianye Rao, Yongdong Li, Department of Electrical Engineering Tsinghua University, "Investigation of Control Method for a New Hybrid Cascaded Multilevel Inverter", The 33rd Annual Conference of the IEEE Industrial Electronics Society (IECON).

- [8] Dr. Sudha Arora, Vikas Deep Juyal, Dept. of Electrical Engineering, G.B.P.U.A&T Pantnagar, Uttarakhand-263145, India, "Power Quality Improvement of a System using Three Phase Cascaded H-Bridge Multilevel Inverters", IEEE International Conference on Recent Advances and Innovations in Engineering (ICRAIE-2016), December 23-25, 2016, Jaipur, India.

- [9] Ebrahim Babaei, Concettina Buccella, Maryam saeedifard, "Recent Advances in Multilevel Inverters and Their Applications—Part I", IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 63, NO. 11, NOVEMBER 2016.