# Efficient Techniques of Adiabatic Logic Design for Low Power Consumption

N. Swamy, Assistant professor swamynallabelli@gmail.com

B. Siva Prasad, Associate professor sivaprasadb@bitsvizag.com

# S. Aruna Kumari

# Assistant professor sarunakumari@gmail.com

**Abstract:** Power utilization assumes a noteworthy job in present day VLSI structure innovation. The interest for low power expending gadgets is expanding quickly and the adiabatic rationale style is said to be an appealing arrangement. This paper explores diverse strategies for planning adiabatic rationales, for example, CMOS adiabatic circuits, ECRL, PFAL, CAL, DFAL, 2N-2P and 2N-2N2P. A great deal of research has been now done utilizing adiabatic procedure. This paper shows an audit of previously mentioned adiabatic inverters in writing from essential components. The recreation results demonstrate the correlation of intensity dispersal between customary CMOS circuits and adiabatic rationale based circuits.

Keywords: Low -power, Adiabatic logic, CMOS, ECRL, PFAL, CAL, Power dissipation, Recovery logic

# **1. Introduction**

The power utilization of the electronic gadgets can be decreased by embracing distinctive plan styles. Adiabatic calculation has been broadly contemplated as a low - power design technique. In the ongoing years, a few adiabatic or vitality recuperation rationale designs have been proposed [1-6]. They have accomplished critical power investment funds contrasted with regular CMOS circuits. In regular CMOS level-reestablishing rationale, the exchanging occasion of circuits with rail-to-rail yield voltage swing causes a vitality exchange from the power supply to the yield hub or from the yield hub to the ground which causes more power dissipation. To build the vitality effectiveness of the rationale circuits, different measures can be presented for reusing the vitality drawn from the power supply. To build the vitality effectiveness of the logic circuits, different measures can be presented for reusing the vitality drawn from the power supply. A tale class of logic circuits called adiabatic rationale [1], [2] offers the likelihood of further lessening the vitality disseminated amid the exchanging occasions, and the likelihood of reusing, or reusing, a portion of the vitality drawn from the power supply. The yields of adiabatic circuits are just legitimate amid a specific period of the power clock cycle.

# 2. Adiabatic logic

This term originates from thermodynamic framework which implies no warmth exchange from framework to condition and the other way around. Adiabatic rationale is otherwise called "vitality recuperation rationale" as it reuses the vitality. It shows that as opposed to disseminating the put away vitality amid the charging procedure, it reuses the vitality back to the power supply in this way decreasing the power dissipation. Adiabatic strategies depend on adiabatic rationale standard. Following area portray how the adiabatic rationale varies from customary exchanging Full-adiabatic circuits don't have non-adiabatic misfortune, yet they are substantially more intricate than semi adiabatic circuits. Here all the charge on the heap capacitance is recouped by the power supply. Completely adiabatic circuits have issues as for the working velocity and the power clock synchronization. One of them is SCRL which is depicted underneath.

#### 2.1. Power Dissipation while Discharging and Charging

#### 2.1.1 Conventional Logic Switching

In customary CMOS level-reestablishing logic which utilizes the consistent voltage source VDD, the exchanging occasion of circuits with rail-to-rail yield voltage swing causes a vitality exchange from the power supply to the yield hub or from the yield hub to the ground.

Fig.1. Conventional CMOS Charging and Discharging

In the period of 0-to-VDD progress of the yield, the aggregate yield charge Q= CL VDD is drawn from the power supply at a consistent voltage. Along these lines, vitality E = CL VDD2is drawn from the power supply amid this progress. Charging the yield hub capacitance to the voltage level VDD implies that toward the finish of the progress, the measure of put away vitality in the yield hub is  $E = \frac{1}{2}$  CL VDD2. Thus, half of the infused vitality from the power supply is scattered in the PMOS organize while just a single half is conveyed to the yield hub [3]. Amid a resulting VDD - to-0 progress of the yield hub, no charge is drawn from the power supply and the vitality put away in the heap capacitance is dispersed in the NMOS arrange. To diminish the dispersal, the circuit originator can limit the exchanging occasions, decline the hub capacitance, decrease the voltage swing, or apply a blend of these strategies.

Fig.2. CMOS Inverter

However in every one of these cases, the vitality drawn from the power supply is utilized just once before being dispersed. This adiabatic rationale utilized beat control supplies of inverse stages have 3V dc.

## 2.2. Adiabatic Switching

To expand the vitality proficiency of the rationale circuits, the circuit topology and the working standards must be changed according to the need emerges. The measure of vitality reusing [1] reachable utilizing adiabatic methods is likewise dictated by the procedure innovation, exchanging speed, and the voltage swing. This circuit can be changed to recuperate flag vitality by using sloped power-clock motions rather than static working voltage and ground. A case of such vitality recuperating 1n1p-rationale [3] inverter is appeared if Fig. with the relating double check waveforms in Fig., which can include vitality into the circuit and recuperate it back to the clock.

Fig.3. Adiabatic Charging and Discharging

Figure 3 demonstrates the model of an adiabatic rationale appearing perfect switch in arrangement with opposition and two correlative voltage supply tickers. Consistent voltage source is utilized in customary CMOS rationale to charge the heap capacitance however if there should be an occurrence of adiabatic rationale exchanging circuits we utilize steady current source rather than steady voltage source. Figure3. Portrays unmistakably how this can be accomplished with resulting clarification.

#### **3. Different Adiabatic Techniques**

Diverse rationale styles of adiabatic circuits have been proposed throughout the years and the multifaceted nature of circuits likewise shift as per configuration by number of activity clock, single-double rail style, charging and releasing way and so on. Adiabatic rationale helps in the decrease of the power scattering of the circuit and this paper audits the proposed adiabatic methods and circuits are intended to demonstrate lessened power dispersal.

Adiabatic rationale structures are for the most part of two sorts:

- Partially adiabatic rationale, which is delegated Efficient charge recuperation rationale (ECRL), Quasi Adiabatic Logic(QAL), Positive input adiabatic rationale (PFAL), NMOS vitality recuperation rationale, True single stage adiabatic rationale (TSAL)

- Fully adiabatic rationale, Classified as Pass transistor adiabatic rationale, 2 Phase adiabatic Static CMOS rationale (2PASCL), Split rail charge recuperation rationale (SCRL).

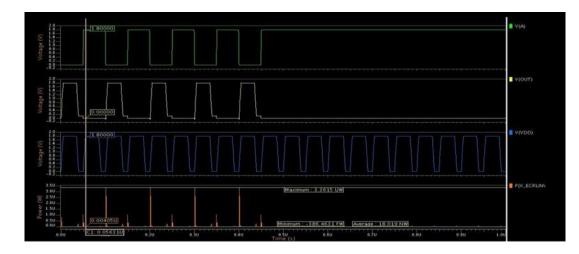

- Input requirement for conventional CMOS inverter is prearranged as DC input pulse signal V1 = 3V, V2 = 0V, td = 0, tr = 1ns, tf = 1ns, pulse width is 160n and period is 320n. Constant power supply 3V is to the PMOS device. Equivalent input pulse signal given to the adiabatic logic inverters with pulsed power supply

ranges of V1 = 3V, V2 = 0V (V1 = 0V, V2 = 3V when two pulsed power supplies used) td = 0, tr = 40ns, tf = 40ns, pulse width is 40n and period is 160n.

## **3.1. ECRL**

The logic work in effective charge recuperation rationale structure is evaluated by sets of draw down gadgets (NMOS) likewise through PMOS gadget, ECRL can't get the power clock which performs like semi adiabatic rationale style . ECRL executes a strategy of performing concurrent pre-charge and assessment.

- Logic work in ECRL inverter is, when control clock goes up beginning from zero to VDD, yield remains in ground level and when control time comes to at VDD, yields 'out' and '/out' hold rationale esteem zero and VDD separately. This yield esteems will be utilized for the following stage.

- When control clock tumbles from VDD to zero, '/out' restores its vitality to control clock which recoups the conveyed charge.

Fig. 5 ECRL logic Invertor

Fig. 6 Simulated Waveform

## 3.2. CAL

Timed CMOS Adiabatic Logic (CAL) is another adiabatic rationale which is worked by single-stage control check supply in adiabatic mode and by a dc control supply in non-adiabatic mode. Consequently this can be worked in non-adiabatic and adiabatic modes. CAL structure is appeared in Figure. CAL in adiabatic mode has single stage control clock is contrasted and another adiabatic rationale inverters. This adiabatic circuit has huge decrease in power dispersal 2.48E-24W.

**Fig.7 CAL Invertor**

## 3.3. SCRL

A customary, static, rationale structure does not require double rail input. It is conceivable to manufacture asymptotically zero power CMOS utilizing this strategy and 'Split-Level Charge Recovery Logic' (SCRL) based inverter is appeared beneath circuit. Charm stage control clock supplies are actualized here, where control clock, information and yield voltage are at a voltage of VDD/2 when inverter is out of gear condition.

**Fig.8 SCRL Inverter**

Rationale work in SCRL is controlled by applying the information V2 and afterward control clock supply voltages v4 are changed so as to apply a voltage of VDD as shown in below diagram. Power clock voltage level is brought to a level of VDD/2 when valid output is available.

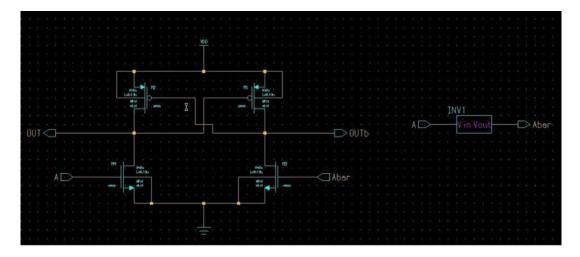

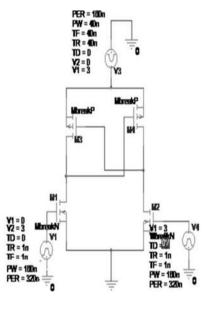

#### 3.6. 2N- 2P

As name represents, this circuit has 2 NMOS devices and 2 PMOS devices which is using differential logic gives both a logic function and its complement. 2N-2P differential buffer/inverter is shown in the figure. Where power clock supply is connected to cross - coupled PMOS devices and each NMOS devices get the corresponding positive and negative polarity inputs. Four phases of circuit function has been shown in following fig.

Fig.9 2N\_2P Inverter

• Outputs are complementary when inputs are low during reset phase and power clock supply ramps down. Output is high, when PMOS Device is detained by the

low output, will "ride" the ramp down as a result, at the end of reset phase both outputs are low.

- Power-supply remains low in wait phase which continues the outputs low and the inputs are estimated.

- The power supply ramps up in evaluate phase and the outputs will evaluate to a complementary state. At the end, the outputs will be complementary.

- The power supply clock continues high in the hold phase while inputs ramp down to low.

#### 3.7. Quasi Inverter

Quasi inverter is a partially adiabatic logic inverter in which shown below circuit has pulsed power clock supply instead of DC supply like CMOS inverter shown first. Compare with conventional logic this adiabatic logic inverter gives reduced power dissipation of 6.37E-20w.

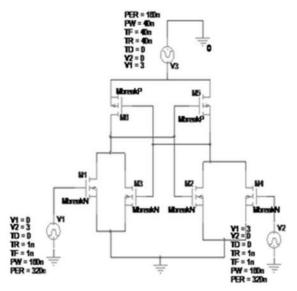

#### 3.8. 2N-2N2P

The Quasi-adiabatic irreversible latches based 2N-2N2P has pair of cross coupled PMOS devices, reduces the standard energy on output to 0.5CVT2 as opposed to conventional 0.5 CV2. Through the PMOS transistor, energy on the output node capacitance is discharged into power clock until the voltage on node decreases to VTP. This adiabatic logic circuit uses PMOS devices to recover major portion of the total energy.

To expand the vitality productivity of the rationale circuits, different measures can be presented for reusing the vitality drawn from the power supply. An epic class of rationale circuits called adiabatic logi coffers the likelihood of further diminishing vitality dispersal amid the exchanging occasions, and the likelihood of reusing, reusing,

Fig.10. 2N-2N2P Inverter

| S.No. | Inverter       | Transistor's Required | <b>Power Dissipation</b> |

|-------|----------------|-----------------------|--------------------------|

| 1     | CMOS inverter  | 2                     | 8.13E-20w                |

| 2     | ECRL Inverter  | 4                     | 2.48E-24w                |

| 3     | PFAL Inverter  | 6                     | 1.23E-23w                |

| 4     | QUASI Inverter | 2                     | 6.37E-20w                |

| 5     | DFAL Inverter  | 3                     | 8.13E-20w                |

| 6     | SCRL Inverter  | 2                     | 8.13E-20w                |

| 7     | CAL Inverter   | 8                     | 2.48E-24w                |

| 8     | 2N-2P          | 4                     | 2.48E-24w                |

| 9     | 2N-2N2P        | 6                     | 4.64E-20w                |

Table 1.Comparison of number of transistor required for Inverters and power dissipation

## 4. Conclusion

Thus, it has been observed that, Adiabatic CMOS circuits can be successfully used to implement a digital circuit design using gradually rising and falling power-clock. Either retractile cascade power clocks or multiple phase power clocks with memory schemes can be used in large circuit design with low power consumption. Their rate control sparing shows their amazingness over regular circuits. Additionally, in the proposed rationale, the transistor tally and the territory per chip is likewise generally lesser. The future extent of this work is that these squares reproduced can be utilized with higher number of information and yield lines can be built by falling the proposed squares. The essentials of adiabatic calculation and the most notable adiabatic rationale families are depicted. New adiabatic design at high frequency may be aimed so that adiabatic circuit may be used in many high frequency applications also.

The adiabatic circuit design can be improved by introducing conventional power supply. Further to improve switching speed of adiabatic circuit as compare to CMOS logic new adiabatic circuits with better switching speed can be designed.

## 5. References

- 1. Ashmeet Kaur Bakshi, Manoj Sharma, "Design of basic gates using ECRL and PFAL", International Conference on Advances in computing, communication and informatics, IEEE, 2013

- Teichmann, Philip "Adiabatic Logic, Future Trend and System Level Perspective", XVII, 166p., Springer; 2012

- Visvesh S. Sathe, Member, IEEE, Juang-Ying Chueh, Member, IEEE, and Marios C. Papaefthymiou, Senior Member, IEEE"Energy-Efficient GHz-Class Charge-Recovery Logic" Ieee journal of solid-state circuits,vol.42,no.1,January 2007

- 4. Arun Kumar, MAnoj Sharma, "Design and analysis of MUX using Adiabatic Techniques ECRL and PFAL", International Conference on Advances in computing, communication and informatics,IEEE,2013

- Fang fang Zang, Jianping Hu\*, Wei Cheng." Power-Gating Scheme and Modeling of Near-Threshold Adiabatic Flip-Flops". Telkomnika Indonesian Journal of Electrical Engineering Vol.12, No.1, January 2014, pp. 89 ~ 97

- 6. Vojin G. Oklobd<sup>\*</sup>zija, Fellow, IEEE, Dragan Maksimovi<sup>\*</sup>c, Member, IEEE, and Fengcheng Lin<sup>\*</sup> Pass-Transistor Adiabatic Logic Using Single Power-Clock Supply<sup>\*</sup> Ieee transactions on circuits and systems-II:analog and digital signal processing,vol.44,no.10,October 1997

- 7. S. Kang and Y. Leblebici (2003), Cmos Digital Integrated Circuits Analysis and Design,